前言

补基础

目录

- 1. 量化误差(Quantization Error)

- 2. DNL

- 3. INL

- 4. 偏移、增益误差(offset、gain error)

- 5. SNR

- 6. ENOB

- 7. ADC的输入阻抗

- 8. ADC的转换时间

- 9. 参考资料

1. 量化误差(Quantization Error)

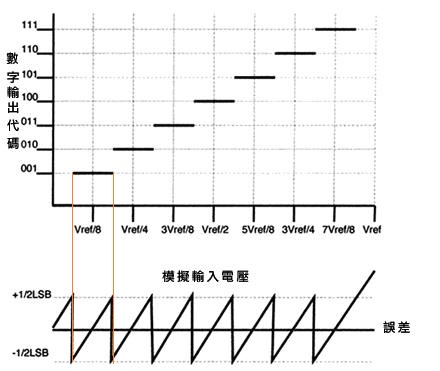

用简单3bit ADC来说明。

输入电压被数字化,以8个离散电平来划分,分别由代码000b到111b去代表它们,每一代码跨越Vref/8的电压范围。

代码宽度一般被定义为一个最低有效位(Least Significant Bit,LSB)。

NOTE:code width(n) = v(n+1) - v(n)

这里v(n+1)表示输出代码由n跳变为n+1时对应的模拟输入电压,v(n)表示输出代码由n-1跳变为n的模拟输入电压。v(n+1) - v(n)表示输出代码n的代码宽度。

若假定Vref=8V时,每个代码之间的电压变换就代表1V。如图中橙色线所示,即当输入电压为0.5V或者1.5V时,ADC输出的结果都是1V(001b),这里的误差称为量化误差。

量化误差是±0.5LSB,但是ADC实际的LSB应该参考ENOB而不是分辨率位数。

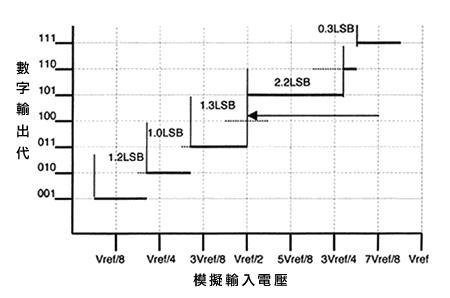

2. DNL

DNL,即微分非线性,表征的是我们ADC的实际刻度与理想刻度之间的差值。

DNL是ADC的相邻代码之间的实际差值与相邻代码之间的理想差值的误差。

比如说我们手中普通的尺子,正常情况下一小格长度应该是标准的1mm。但是由于生产精度,材质,受力引发的形变等影响,尺子上上标注的1小格长度可能并不是标准的1mm,可能是0.98mm,也可能是1.02mm。

比如说我们尺子上的某两个相邻的刻度线之间长度已经变成了0.98mm,那么我们就可以说“A刻度线到B刻度线的DNL是(0.98-1)/1=0.02 LSB”,这里的LSB就是指我们的一个最小刻度对应的长度是多少,对于一般的尺子就是1mm。

将尺子转成ADC,即:

从001b到010b过渡过程的DNL为0LSB,因为刚好为1LSB。

从000b到001b过渡过程就有个0.2LSB的DNL,因为此时有1.2LSB的代码宽度。

NOTE:如果在datasheet中没有清楚说明DNL参数的话,可视该转换器没有漏码,即暗示它有优于±1LSB的DNL。

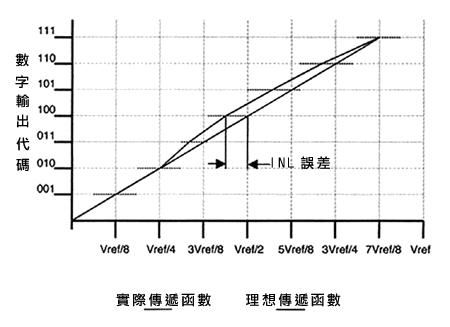

3. INL

INL,即积分非线性,表征的是大信号的线性误差,是指ADC给定输入所包含全部DNL的累计代数和。

INL是ADC的所有代码点上对应的理想模拟量和真实模拟量之间误差最大的那一点的值。

如图,即本来100b对应的理想模拟量是Vref/2,但是真实模拟量介于3Vref/8~4Vref/8,则说这里存在INL误差。出现这种情况的原因。

从整个输出代码来看,每个输入电压代码步距差异累积起来以后和理想值相比会产生一个总差异,这个差异就是非线性积分误差。

NOTE:

INL(n) = INL(n-1) + (DNL(n) + DNL(n-1)) / 2

即

INL(n) = DNL(1) + DNL(2) + ….DNL(n) / 2

4. 偏移、增益误差(offset、gain error)

这两个参数主要是用来校准ADC的模拟前端的。

目的是让ADC的编码深度能够最大限度的不压缩额定输入信号的幅度,以减少模拟前端的误差造成的信号损失。

可以简单的理解为:

- offset是校准模拟前端的准位,要么是0电平的参考点,要么是中间值的参考点;

- gain是校准模拟前端的信号幅度,也就是输入最大额定信号的编码要对应最大编码值。

这两部分的校准都需要对已知信号进行采样并且与已知信号对应的编码值进行比对,然后调整的,一般是先校准offset,然后校准gain值。当然两个值的校准要用到不同的参考信号。offset与gain是在同一个位置上做的,不需要分先后。

NOTE:

若增益误差为11%FSR,根据原始数据测算ADC电压为3V,则需要校准3 * 1.11 = 3.33V

5. SNR

信噪比(SNR)就是信号能量和量化噪声能量之比,但是这对于ad来说只是理想情况,即只考虑量化噪声,而实际情况是热噪声,量化噪声以及谐波失真都在干扰信号,于是实际测量AD性能的时候用的更多的是SNDR(信噪失真比),即信号与(热噪声,量化噪声以及谐波失真能量之和)的比值。

可以将量化后的信号进行fft分析后计算得到。这个量用于衡量ADC转换时候信号被噪声影响了多少。

而SFDR(无杂散动态范围)是fft分析频谱中信号幅度与最大谐波之间的距离(可以直接从频谱图中读出),这个距离越大,说明ADC的动态性能越好,就是说转换越接近线性。

一般来说SFDR的值会远大与SNDR,而当趋于理想情况时SNDR≈SNR,大概就是这么个关系。

6. ENOB

ENOB真实的反映了我们ADC的有效位数是多少,让我们可以真正了解这个ADC的真实性能。

7. ADC的输入阻抗

一般在我们使用ADC时,尤其是MCU内部自带的ADC,都会说明一下对外面信号源阻抗的要求,如注明我们的ADC对外面的输入阻抗要求是10K。

这项参数意味着我们的被测信号源的内阻不能大于10K,否则我们的输出精度将无法被保证。原因是芯片内部的ADC电路前面有一个采样保持电路,假如外面内阻太大会直接影响到这个电路的充放电,从而影响到我们最终的转换精度。

8. ADC的转换时间

以SAR ADC为例,一般MCU内部自带的ADC可有有几个配置可以影响到ADC的转换速度:转换位数N,ADC时钟f,采样保持时间t。那么我们的ADC转换一次的时间就是N*1/f+t,这就是我们ADC转换一次的时间。

我们会发现有的MCU可以选择10bit或者12bit输出模式,有的人会想这是不是多此一举,实际上从上面的公式可以看出,我们的转换位数会影响到我们ADC的转换速度的。

另外说一句,对于同一个ADC,假如我们的转换速度设置很快也会降低我们的ADC精度,因此你会发现所有ADC 的Datasheet中的转换精度描述一栏的测试条件栏中会加上对转换速度的限制条件。所以,我们在使用ADC时,若没有速度的要求,建议将ADC的转换速度适当降低,以换取较为准确的精度。